芯粒異構集成給半導體行業帶來一次重大升級,能有效解決芯片設計制造中的諸多瓶頸。然而,高密度集成在降低算力芯片成本的同時也面臨功耗顯著增加、散熱困難等技術挑戰,熱管理成為提升芯片性能的關鍵問題。如何針對芯粒異構集成的復雜性,提出新的熱仿真方法,這對Chiplet熱管理技術提出了新的要求。

針對以上問題,微電子所EDA中心多物理場仿真課題組構建了芯粒集成三維網格型瞬態熱流仿真模型,能夠實現Chiplet集成芯片瞬態熱流的高效精確仿真,為芯粒異構集成溫度熱點檢測和溫感布局優化奠定了核心技術基礎。同時,課題組在集成芯片電熱力多物理場仿真方面進行布局,開展了直流壓降、熱應力和晶圓翹曲仿真等研究工作。

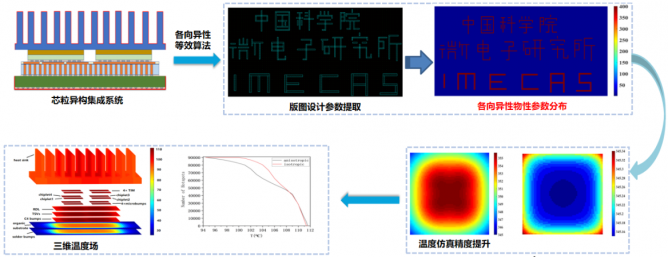

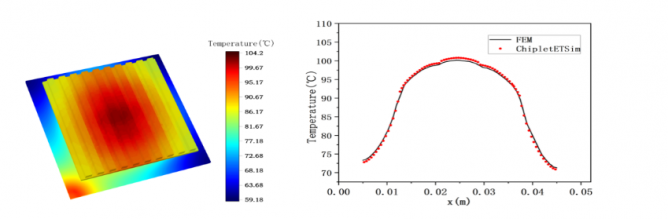

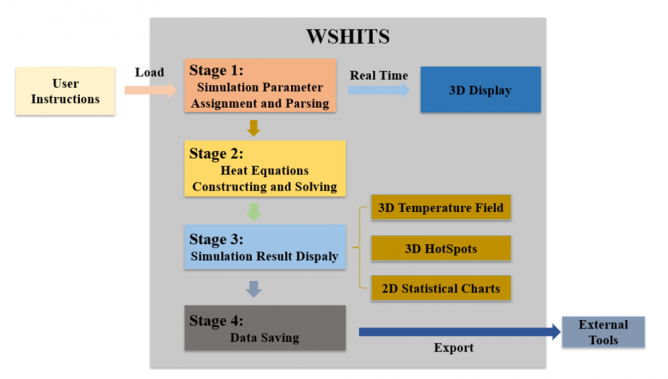

近期,課題組在Chiplet熱仿真工具方面取得新進展。通過對重布線層(RDL)、硅通孔(TSV)和凸點陣列進行各向異性等效,構建了從GDS版圖到系統級封裝的跨尺度各向異性熱仿真模型,在提升仿真模型精度的同時優化了集成芯片溫度熱點檢測方法。同時,構建了芯粒異構集成電熱耦合仿真模型,支持復雜互連結構物性參數等效,實現了電熱雙向耦合高效計算,可準確描述集成芯片焦耳熱效應下的溫度變化行為。此外,基于以上模型和算法研究進展,將熱仿真方法拓展至更大尺度,自主研發了晶圓級熱仿真模擬器。該模擬器能夠為芯粒異構集成芯片提供更大尺度的熱仿真分析,同時支持散熱器流體動力學模型設計,仿真結果更接近實際應用場景的潛在溫度熱點預測,有助于優化熱設計仿真流程。與有限元方法相比,模擬器單元數量減少了2.78倍,運行時間減少了25.9倍,相對誤差為0.38%。目前,課題組與國內知名企業開展了熱仿真關鍵技術合作,相關模型和算法正在進行應用驗證。

以上研究得到了中國科學院戰略性A類先導專項、國家自然科學基金重大研究計劃、國家重點研發計劃、中國科學院青年交叉團隊等項目支持,研究成果先后發表在熱力學頂級期刊《Applied Thermal Engineering》 (A wafer-scale heterogeneous integration thermal simulator, DOI:10.1016/j.applthermaleng.2025.125459) 和微電子系統權威期刊《IEEE Transactions on Very Large Scale Integration (VLSI) Systems》(A multiscale anisotropic thermal model of chiplet heterogeneous integration system, DOI:10.1109/TVLSI.2023.3321933;An electrical-thermal co-simulation model of chiplet heterogeneous integration systems, DOI: 10.1109/TVLSI.2024.3430498)上。微電子所研究生王成晗、馬曉寧為上述論文第一作者,微電子所徐勤志研究員和李志強研究員為上述論文通訊作者。

圖1 各向異性熱仿真

圖2 電熱耦合仿真

圖3 熱仿真模擬器

(來源:中國科學院微電子研究所i)