在現代電子工業中,熱管理是一個關鍵的挑戰。半導體器件產生大量的廢熱,這些廢熱必須在規定的溫度范圍內有效地消散,以維持器件的性能和可靠性。這些熱量通過具有顯著熱阻的層和界面從器件熱點傳遞到換熱器進行散熱。最近的研究主要集中在用高導熱材料取代普通襯底以降低總體熱阻。金剛石的各向同性是所有塊狀材料中最高的,這使它成為芯片冷卻的理想散熱材料。模擬表明,薄金剛石可以將熱阻降低20%。然而,金剛石冷卻器在實際應用中的進展仍然有限。實現低熱邊界阻(TBR)的金剛石近結集成是一個關鍵的挑戰。

金剛石在器件上的成功集成在很大程度上取決于金剛石/半導體連接接口的設計。這些接口的優化對于最小化TBR,同時確保足夠的機械穩健性以承受長期可靠運行至關重要。此外,應避免高加工溫度,因為它們對實現與半導體制造工藝。此外,在芯片封裝過程中,金剛石/半導體連接需要表現出足夠的熱穩定性,以承受隨后的焊料回流(溫度高達300°C)。

由于金剛石和半導體在晶格常數、硬度、德拜溫度和熱膨脹系數(CTE)等方面存在廣泛的不匹配,因此解決這些問題需要付出專門的努力。在過去的幾十年里,人們進行了各種各樣的嘗試,其中涉及三種主要的技術方法:在金剛石上外延生長半導體;化學氣相沉積法(CVD)直接生長金剛石以及金剛石與半導體的結合。然而,目前這些方法面臨著TBR大、加工溫度高、可靠性低和效率有限等挑戰。

近日,廈門大學鐘毅和華為技術有限公司赫然聯合針對解決現代電子器件的熱管理問題取得最新進展。該文提出了一種集體晶圓級鍵合技術,通過反應性金屬納米層在 200°C 下連接多晶金剛石和半導體。由此產生的硅/金剛石連接具有 9.74m2GW-1的超低 TBR ,大大優于傳統的芯片連接技術。這些連接還表現出卓越的可靠性,可承受至少1000次熱循環和1000小時的高溫/潮濕考驗。這些特性與所設計的金屬夾層的再結晶微觀結構有關。該演示代表了金剛石在半導體上的低溫和高通量集成的進步,有可能使目前受熱限制的電子應用成為可能。研究成果以“Low-temperature bonding of Si and polycrystalline diamond with ultra-low thermal boundary resistance by reactive nanolayers”為題發表在《Journal of Materials Science & Technology 》。

圖文導讀

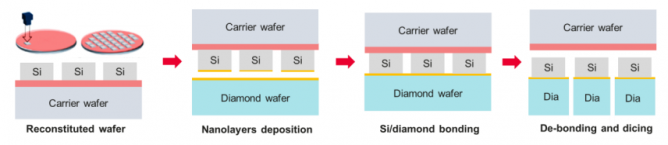

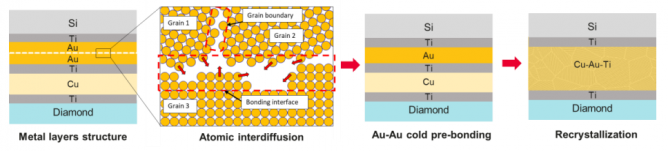

圖1. 晶圓級硅/金剛石鍵合工藝示意圖。

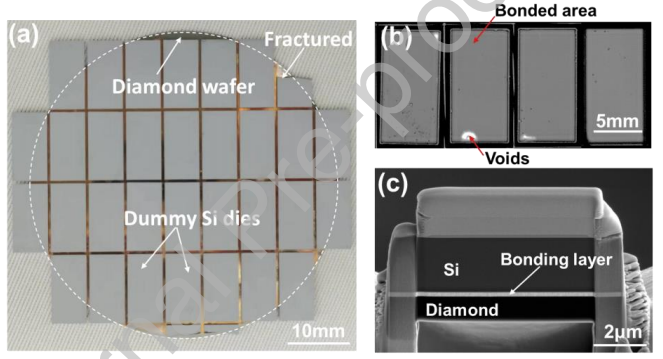

圖2. (a) 2英寸金剛石晶片與Si模結合的照片,(b)掃描聲顯微鏡測定的典型鍵合孔隙率,(c)截面顯微結構顯示出一條均勻的結合線。

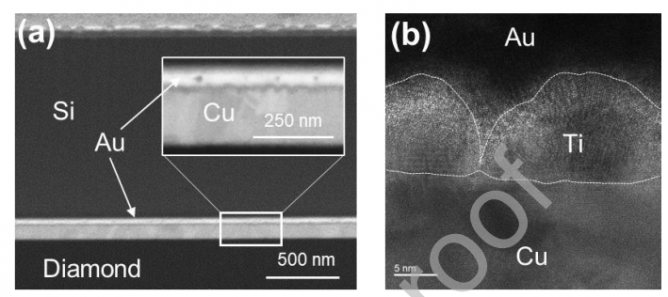

圖3. (a) Si/金剛石結合層的TEM分析,(b, c) Si/metal和金剛石/metal界面的高分辨率TEM圖像,(d)掃描線上EDS元素濃度分布圖,(e)鍵合樣品的XRD譜圖,表明CuAu固溶相的形成。

圖4. (a)室溫預鍵合后的金剛石/硅界面微觀結構(b) Ti納米層中明顯的晶界。

圖5. Si/金剛石連接通過兩步工藝實現:室溫AuAu預鍵合和低溫Cu-Au-Ti再結晶。

圖6. (a)電子封裝中的TBR示意圖和(b)相應的溫升。

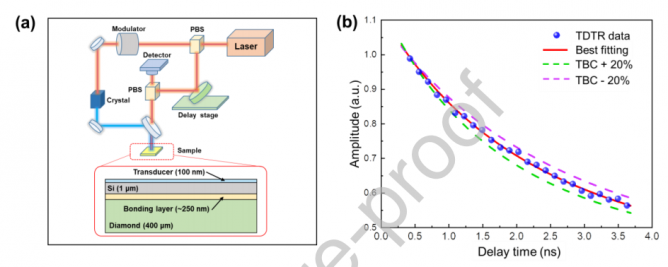

圖7. (a) TDTR的設置示意圖和測試樣品的結構,(b) TDTR幅度信號作為延遲時間的函數。