晶體管是三端電子器件,其發展的主要動力是由“摩爾定律”主宰的微縮技術:通過使晶體管尺寸越來越小,越來越多的晶體管可以被制造到同一芯片中,從而可以實現更復雜的功能。然而,隨著溝道長度進一步的縮短至10 nm工藝節點以下,微縮技術逐漸顯示出了越來越多難以克服的問題。其中最顯著的就是柵極電場對硅溝道的調控性能開始弱化,導致無法避免的短道效應和巨大的關態能耗。

具有超薄厚度的單原子層晶體管呈現出對短溝道效應的有效抑制,在小尺寸電子器件中顯示出巨大的潛力。然而,亞1納米厚度的單層晶體管只能在晶格結構相對穩定的少數二維半導體上實現。而對于多種結構不穩定的二維半導體,單層溝道表面無法和光刻工藝及金屬化工藝相互兼容,難以形成穩定的電學接觸。

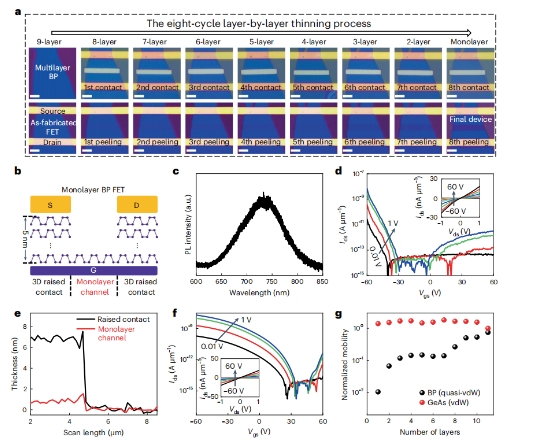

針對這一挑戰,湖南大學物理與微電子科學學院劉淵教授團隊報道了一種三維凸起電學接觸結構。通過逐層機械剝離,晶體管的溝道區域可以逐漸減小到單層厚度,而不會破壞其晶格。同時接觸區仍然保持三維的體材料性能。通過這一方式,團隊實現了多種具有亞1納米厚度單層晶體管。同時,團隊發現黑磷晶體管的載流子遷移率隨著體厚度的減小而急劇下降,表現得更像傳統的塊狀半導體而不是純粹的范德華層狀半導體。該研究展示了各種具有三維凸起接觸的二維單層晶體管,提供了一種構建橫向同質結或超晶格的通用方法。

單層二維BP和GeAs晶體管的電學性能

該研究成果以“Monolayer black phosphorus and germanium arsenide transistors via van der Waals channel thinning”為題發表在《自然·電子學》雜志上(s41928-023-01087-8, 2023),湖南大學物電院為第一單位,物電院博士生李婉瑩為第一作者,劉淵教授為通訊作者,合作單位包括中科院微電子所與武漢大學。該工作得到了來自國家自然科學基金、國家重點研發計劃等項目的資助。

(來源:湖南大學)