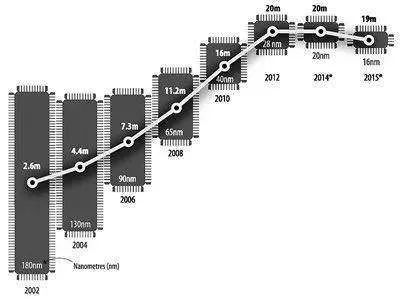

隨著晶體管變得越來越細小,臺積電采用新工藝技術上的速度也變慢了,以往大概每兩年就會進入一個新的制程節點,現在則要等更長的時間。

為了滿足其所有客戶的需求,臺積電不得不繼續提供其制造工藝的半節點、增強和專業版本。

臺積電積極奔赴下一代工藝節點

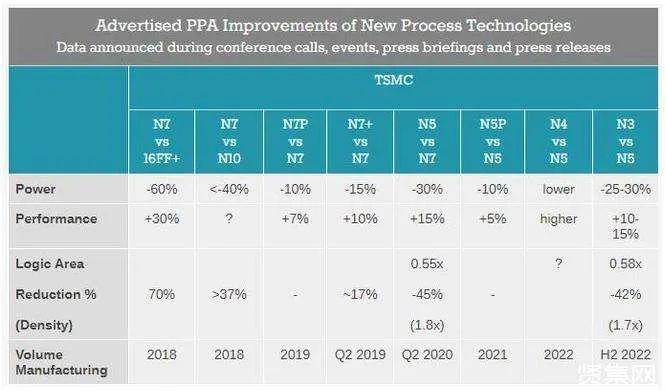

臺積電在過去 20 年左右的成功很大程度上取決于該公司能夠提供一種新的制造技術,每年都會改進 PPA(功率、性能、面積),并每 18 至 24 個月推出一個全新的節點,同時保持可預測的高水平產量。

但隨著現代制造工藝的復雜性達到前所未有的水平,在保持可預測的產量和簡單的設計原則的同時保持創新步伐變得越來越困難。

眾所周知,臺積電和三星電子現在的主力芯片產品都是采用的5nm制程工藝技術,當然還有大量的使用的是7nm制程技術。而無論是蘋果公司還是三星電子的手機產品已經大量使用了5nm制程的產品。

在臺積電第一季度財報電話會議上表示,正全力以赴地開發下一代工藝節點。計劃在今年晚些時候將投產首批 3nm工藝,有了臺積電的N3 節點,N5(5 納米級)爬坡和 N3(3 納米級)爬坡之間的差距將增加到 2.5 年左右,這可能會給代工廠的主要客戶蘋果帶來一些挑戰。

同時,N2的節奏將延長至三年左右,這在很大程度上意味著臺積電節點發展戰略的戰略轉變。

引入改進的3nm節點

臺積電的 N3 將在 N5 的基礎上實現全節點改進,包括提高 10% ~ 15% 的性能、降低 25% ~ 30% 的功率以及高達 1.7 倍的邏輯晶體管密度。為此,它將使用超過 14 個極紫外 (EUV) 光刻層(N5 使用多達 14 個,預計 N3 將使用更多),并將為深紫外光刻 (DUV) 層引入某些新的設計規則。

臺積電將在下半年開始使用其 N3 節點增加芯片的生產,并將在 2023 年初向一個(或多個)客戶交付第一批商用芯片,屆時它將獲得第一筆 N3 收入。

雖然臺積電的 N3 工藝技術專為高性能計算(臺積電用來描述 CPU、GPU、FPGA、ASIC 等應用的術語)和智能手機而設計,但有證據表明該節點具有相當狹窄的工藝窗口,這將使芯片開發人員難以達到所需的規格。這是一個問題,因為它增加了收益時間并最終降低了利潤率。

為了解決這個問題,臺積電開發了 N3E 版本的技術,該技術 擴大了工藝窗口并提供了對 N5 的改進。

N3工藝的效果會如何

今年下半年,臺積電將把N3工藝投入生產。臺積電預測,HPC(高性能計算)將是其今年增長最快的領域。上一季度HPC產生了41%的收入,僅比智能手機產生的40%略高。物聯網和汽車排在第三和第四位,分別創造了8%和5%的收入。

臺積電多次強調3nm制程將于2022下半年正式量產。而作為競爭對手的韓國三星也在積極加快3nm量產進程。三星此前表示,采用GAA 架構的3nm制程技術已正式流片(Tape Out)。三星3nm制程流片是與新思科技合作,加速為GAA 架構的生產流程提供高度優化參考方法。

三星3nm制程不同于臺積電或英特爾的FinFET架構,而是GAA架構,三星需要新設計和認證工具,因此采用新思科技的Fusion DesignPlatform。制程技術的物理設計套件(PDK)已在2019年5 月發布,并2020 年通過制程技術認證。

為了穩妥,臺積電繼續沿用FinFET晶體管技術,三星兵出險招,采用更先進的GAA晶體管技術,希望能夠在技術上超越臺積電,但是出品率有多高也非常關鍵。

預計2026年出現2nm芯片

臺積電在 2020 年 8 月首次談及 N2 時,并未透露有關技術或其時間表的許多細節,但表示將建立一個位于臺灣新竹縣寶山附近的全新工廠,用于該節點。

臺積電預計在 2024 年底開始使用其 N2 技術進行風險生產,然后在 2025 年底啟動 HVM,這意味著 2022 年第三季度的初始 N3 量產與 2025 年第四季度的初始 N2 量產之間的差距約為三年。“到目前為止,我們在 N2 方面的進展正在走上正軌,”魏哲家說,“2024年底,N2將進入風險生產;2025年,它將投產,可能接近年底。那是我們的日程安排。”

考慮到現代芯片的生產周期,我們可以肯定地說,臺積電制造的第一批 N2 芯片將在 2026 年初到達消費設備。

結語

顯然,臺積電的全新工藝開發和加速節奏已經增加到 N3 的兩年半,N2 將增加到三年,這可能被其主要客戶認為是一個重大放緩。

同時,N3E 的潛在拉入是一個好兆頭,表明該公司可以相當快地實現其節點內的發展。隨著臺積電三年的新節點開發周期,未來的節點內進步對公司及其客戶來說將比現在重要得多。