近日,京都大學(Kyoto University)宣布,使用SiC半導體集成電路成功演示了Si半導體集成電路無法運行的350°C高溫環境下的基本運行。該結果基于京都大學工學研究生院助理教授金子光明和木本恒信教授的研究團隊。詳情于3月25日在青山學院大學相模原校區于3月22日至26日在線舉行的“第69屆日本應用物理學會春季學術講座會”上公布。

據說 Si 半導體在 250°C 左右會發生故障,無法在更高溫度的環境中工作。因此,期望利用具有更好耐熱性并且甚至可以在大約800°C下工作的SiC集成電路。但是,如果用SiC制造與Si集成電路中的晶體管類似的結構,則特性將由于 SiC 特有的缺陷,難以控制高溫環境下的可靠性,并且存在功耗高的問題。

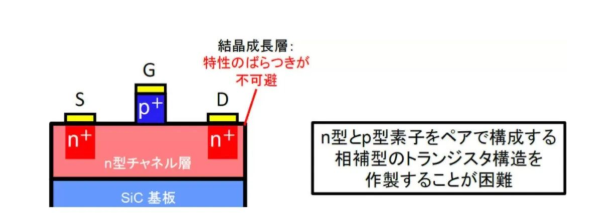

為了解決這些問題,正在開發與Si集成電路中的MOSFET不同的結構的SiC集成電路用晶體管,其中,JFET在電流流動區域沒有MOSFET那樣的物理界面缺陷。因此,作為構成高溫動作的SiC集成電路的晶體管,很有前景。但是,通過一般方法制造的JFET,由于無法像MOSFET那樣在同一基板上構成n型和p型組合的互補電路,因此需要大的待機功率和低功耗,需要進行轉換。

通過一般方法制作的n型JFET的示意圖(晶體生長)

(來源:京都大學新聞發布PDF)

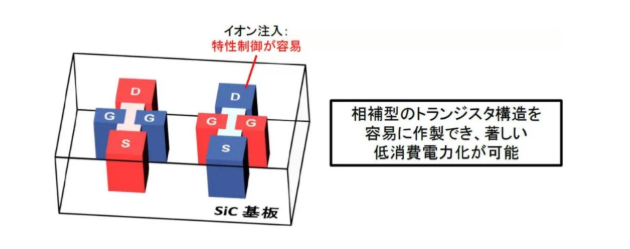

在此背景下,研究團隊提出了獨特的晶體管結構和電路配置。據說它成功地演示了 SiC 邏輯門從室溫到 350°C 的運行,并以低功耗運行。有兩個實現點。首先是實現了在同一襯底上同時制造 n 型和 p 型的技術,這在傳統的通用 JFET 制造方法中是不可能的。通過對整個器件結構進行離子注入進行局部導電型控制,據說它成功地在同一襯底上生產了n型和p型JFET。

通過所提出的方法(離子注入)生產的n型和p型JFET的示意圖(來源:京都大學新聞發布PDF)

第二個是JFET實現了常關型特性,即在沒有電壓施加到柵極端子時不允許電流流動作為晶體管的特性。據說這種特性也很難通過一般的 JFET 制造方法實現,但通過采用雙柵極結構,通過從兩側夾住溝道區域來構成柵極區域,可以制造常關型 JFET。據說已經完成了。

經證實,制造的互補型JFET在室溫至350℃的溫度范圍內正常工作,待機狀態下的功耗最大可抑制在幾十nW以下。研究團隊解釋說,本次研究的優點是本次提出的電路可以使用作為功率半導體的SiC半導體的標準工藝來制造,但我們將繼續進行MOSFET,需要進一步的基礎研究來確定是否JFETs可以通過小型化做得更小、更快、更精密,還需要繼續研究。